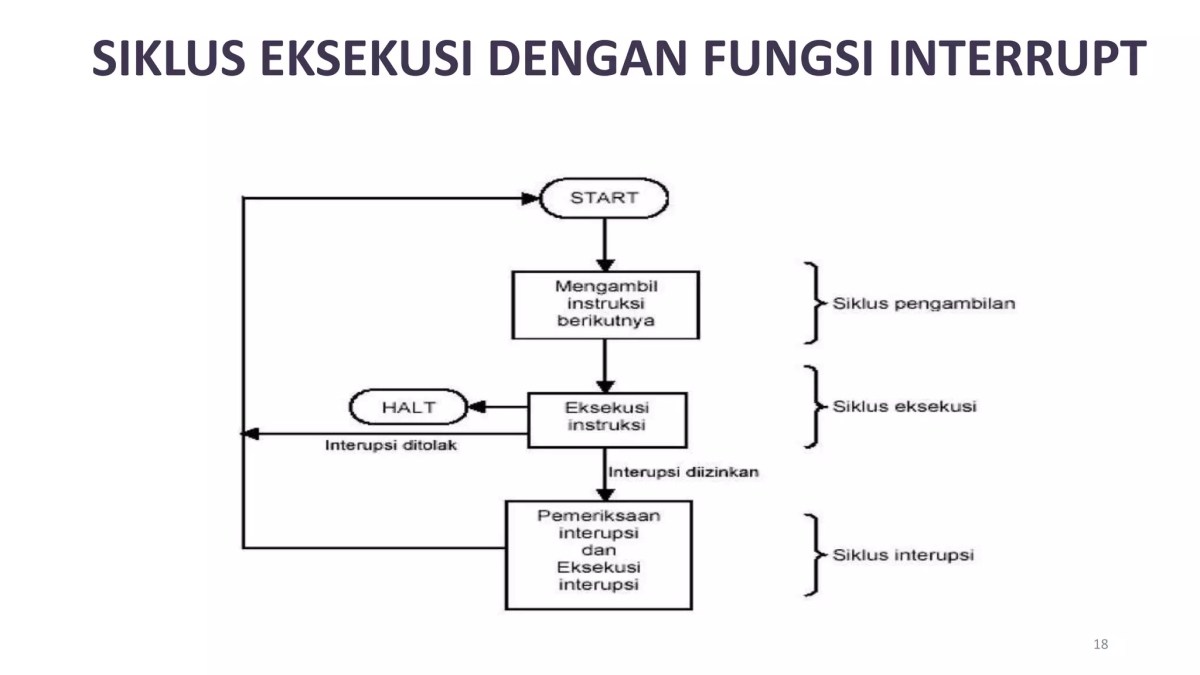

Proses eksekusi instruksi yang berada di register IR itu ibarat detak jantung bagi sebuah prosesor, sebuah ritual mikroskopis yang terjadi miliaran kali setiap detik namun menentukan nasib setiap klik dan ketukan kita. Bayangkan, di balik layar yang mulus, ada sebuah ruang kecil bernama Instruction Register yang menjadi panggung utama dimana kode biner berubah menjadi aksi nyata, sebuah cerita yang jarang diungkap meski menjadi fondasi segala digitalisasi.

Register IR ini berperan sebagai tempat persinggahan sementara bagi sebuah instruksi yang baru saja dijemput dari memori. Di sanalah ia dibedah, dipahami, lalu perintahnya disalurkan ke seluruh penjuru CPU untuk dieksekusi. Proses ini, dari fetch, decode, hingga execute, adalah siklus hidup fundamental yang membuat komputer bisa disebut ‘pintar’, sebuah urutan logis yang telah dirancang dengan presisi tingkat nano.

Pengertian dan Peran Register IR

Bayangkan kamu lagi baca resep masakan. Otakmu akan mengambil satu langkah resep itu, memahaminya, lalu memerintahkan tanganmu untuk mengaduk atau menuang. Dalam dunia CPU, register Instruction Register (IR) adalah tempat “satu langkah resep” itu disimpan sementara untuk dipahami. IR, atau Instruction Register, adalah sebuah register khusus dalam Central Processing Unit (CPU) yang bertugas menampung instruksi yang sedang dieksekusi. Ia adalah titik sentral dalam siklus fetch-decode-execute, menjadi jembatan antara memori tempat instruksi disimpan dan unit kontrol yang akan memerintah eksekusi.

Fungsi utamanya sangat krusial: menjadi penyangga sementara bagi instruksi yang baru saja diambil dari memori utama, sebelum instruksi tersebut diuraikan maknanya. Tanpa IR, CPU akan kebingungan karena harus langsung memproses instruksi yang masih dalam bentuk mentah dari bus data. IR memberikan waktu bagi unit kontrol untuk menganalisis dan menentukan aksi selanjutnya.

Perbandingan Register IR dengan Register Penting Lainnya

CPU memiliki beberapa register dengan peran spesialisasi yang berbeda. Memahami perbedaannya membantu melihat mengapa IR tidak bisa digantikan begitu saja. Berikut tabel yang membandingkan peran IR dengan Program Counter (PC) dan Accumulator (ACC).

| Nama Register | Singkatan | Fungsi Utama | Analoginya dalam Proses Membaca Buku |

|---|---|---|---|

| Instruction Register | IR | Menyimpan instruksi yang sedang diproses/di-decode. | Kalimat yang sedang kamu baca dan pahami di benakmu saat ini. |

| Program Counter | PC | Menyimpan alamat memori dari instruksi berikutnya yang akan diambil. | Jari telunjukmu yang menunjuk nomor baris kalimat berikutnya yang akan dibaca. |

| Accumulator | ACC | Menyimpan hasil sementara dari operasi aritmetika dan logika. | Catatan kecil di samping buku untuk menulis hasil kalkulasi sementara dari cerita yang dibaca. |

Tahapan Awal: Fetch dan Loading ke IR: Proses Eksekusi Instruksi Yang Berada Di Register IR

Sebelum sebuah instruksi bisa dianalisis di IR, ia harus ditemukan dan dibawa ke sana. Proses ini disebut instruction fetch, dan ini adalah langkah pertama yang menentukan dalam setiap siklus mesin. Bayangkan ini seperti kurir yang pergi ke gudang (memori) dengan nomor lokasi (alamat) tertentu untuk mengambil paket (instruksi).

Langkah-Langkah Fetch dari Memori Utama

Source: slidesharecdn.com

Proses pengambilan instruksi adalah tarian yang terkoordinasi antara beberapa komponen. Pertama, nilai dari Program Counter (PC), yang berisi alamat instruksi berikutnya, ditempatkan ke bus alamat. Sinyal kontrol “baca memori” diaktifkan. Memori utama merespons dengan menempatkan data (instruksi) yang tersimpan di alamat tersebut ke bus data. Data pada bus data ini kemudian disalin ke dalam register sementara yang disebut Memory Data Register (MDR) atau langsung ke jalur menuju IR.

Loading dan Ilustrasi Alur Sinyal

Setelah instruksi berada di bus data, langkah selanjutnya adalah memuatnya ke dalam IR. Unit kontrol mengirimkan sinyal “load” atau “enable” khusus ke register IR. Sinyal ini memberitahu IR untuk “menangkap” dan menyimpan nilai yang sedang ada di bus data pada saat itu. Secara visual, alurnya dapat dideskripsikan sebagai berikut: PC mengirim alamat melalui bus alamat menuju memori. Memori mengaktifkan saluran data yang sesuai dan mengirimkan kode biner instruksi melalui bus data kembali ke CPU.

Di dalam CPU, sinyal kontrol “IR-in” aktif, membuka gerbang logika yang memungkinkan data dari bus data mengalir dan terkunci di dalam sirkuit flip-flop register IR. Sementara itu, PC sudah ditambah nilainya (incremented) untuk bersiap mengambil instruksi berikutnya.

Dekode Instruksi di dalam IR

Setelah instruksi aman berada di IR, fase yang paling intelektual dimulai: decoding. Ini adalah proses menerjemahkan rangkaian bit-bit biner yang tampak acak menjadi perintah yang dapat dipahami dan ditindaklanjuti oleh seluruh unit CPU. Jika IR adalah kertas tempat resep ditulis, maka decoding adalah proses membacanya dan memahami bahwa kata “aduk” berarti menggerakkan mixer.

Proses Pemisahan Opcode dan Operand

Unit kontrol akan memeriksa bit-bit tertentu di dalam IR, biasanya bit-bit paling signifikan (paling kiri), yang disebut opcode (operation code). Opcode ini menentukan jenis operasi, seperti ADD, LOAD, atau JUMP. Bit-bit sisanya seringkali merupakan operand, yang berisi informasi tambahan seperti alamat memori data, nomor register, atau nilai langsung (immediate value) yang akan dioperasikan. Proses decoding memisahkan bagian-bagian ini dan mengarahkannya ke komponen yang tepat.

Contoh Interpretasi Blok Instruksi Biner

Mari kita lihat contoh sederhana pada arsitektur hipotesis. Anggap kita memiliki instruksi 16-bit di dalam IR.

– 011 100 000011

Dalam desain ini, 4 bit pertama (0001) adalah opcode. Dari buku panduan set instruksi, unit kontrol tahu bahwa 0001 berarti “ADD”. 3 bit berikutnya (011) menunjuk ke register sumber pertama (misalnya, register R3), dan 3 bit setelahnya (100) menunjuk ke register sumber kedua (R4). Bit-bit terakhir (000011) mungkin adalah offset atau nilai yang tidak digunakan untuk operasi ini. Hasil decodingnya adalah: “Tambahkan isi dari register R3 ke register R4, dan simpan hasilnya di R4”.

Informasi register R3 dan R4 ini kemudian akan dikirim ke unit ALU dan bank register untuk diproses lebih lanjut.

Eksekusi Berdasarkan Konten IR

Hasil decoding dari IR adalah peta jalan bagi unit kontrol. Dengan memahami opcode dan operand, unit kontrol sekarang dapat menyalakan atau mematikan puluhan bahkan ratusan sinyal kendali mikroskopis di dalam datapath CPU. Sinyal-sinyal ini mengatur pembukaan gerbang logika, pemilihan input ALU, penulisan ke register, dan banyak lagi, untuk mewujudkan perintah dari instruksi.

Contoh Prosedur untuk Instruksi Aritmetika dan Load/Store, Proses eksekusi instruksi yang berada di register IR

Untuk instruksi ADD (seperti contoh sebelumnya), unit kontrol akan menghasilkan sinyal untuk: 1) Membaca nilai dari register R3 dan R4 ke saluran input ALU, 2) Mengatur ALU untuk melakukan operasi penjumlahan, 3) Mengaktifkan sinyal untuk menulis hasil kembali ke register R

4. Sementara untuk instruksi LOAD (misalnya, memuat data dari memori ke register), sinyal yang dihasilkan berbeda: 1) Mengirim alamat memori (dari bagian operand IR) ke bus alamat, 2) Mengaktifkan sinyal baca memori, 3) Mengambil data dari bus data ke MDR, lalu 4) Menulis data dari MDR ke register tujuan.

Perbandingan Sinyal Kendali untuk Berbagai Jenis Instruksi

Setiap kelas instruksi membutuhkan pola aktivasi sinyal kendali yang unik. Tabel berikut menyoroti perbedaan kunci dalam pola tersebut untuk beberapa kelas instruksi dasar.

| Jenis Instruksi | Sinyal Kendali ke ALU | Sinyal Kendali ke Memori | Sinyal Kendali ke Bank Register | Sinyal Kendali Lainnya |

|---|---|---|---|---|

| Aritmetika (ADD, SUB) | Aktif (pilih operasi), Baca input A & B | Tidak ada | Tulis ke register tujuan | Update flag status (zero, carry) |

| Logika (AND, OR) | Aktif (pilih operasi logika), Baca input | Tidak ada | Tulis ke register tujuan | Update flag status |

| Branch (JUMP if zero) | Aktif (untuk membandingkan) | Tidak ada | Baca register kondisi | Update PC dengan nilai baru (jika kondisi terpenuhi) |

| I/O (IN, OUT) | Mungkin untuk alamat | Akses ke bus I/O (baca/tulis) | Baca/tulis ke register data I/O | Aktifkan sinyal kontrol perangkat I/O |

Arsitektur dan Implementasi IR

Desain fisik register IR tidak seragam di semua prosesor. Ukuran dan integrasinya sangat dipengaruhi oleh filosofi set instruksi dan kompleksitas prosesor itu sendiri. Lebar bit IR, misalnya, adalah keputusan desain fundamental yang berdampak besar.

Variasi Ukuran dan Integrasi dalam Datapath

Lebar register IR harus setidaknya sama dengan panjang instruksi standar prosesor tersebut. Pada prosesor RISC dengan instruksi tetap 32-bit, IR-nya juga akan selebar 32-bit. Pada prosesor CISC seperti x86 dengan instruksi variabel (dari 1 byte hingga 15 byte), IR mungkin lebih kompleks, kadang berupa buffer yang bisa menampung beberapa byte sebelum decoding penuh. Dalam datapath, IR terhubung langsung ke bus data dari memori.

Outputnya terhubung ke decoder instruksi di unit kontrol, dan bagian operand-nya seringkali terhubung ke multiplexer yang mengarah ke unit alamat, bank register, atau generator konstanta.

Pengaruh Teknologi Pipelining

Pipelining mengubah dramatis cara kita memandang IR. Dalam CPU pipelined, siklus fetch, decode, execute berjalan tumpang tindih. Artinya, ketika instruksi A sedang dieksekusi, instruksi B sedang didecode di IR, dan instruksi C sedang di-fetch. Ini menimbulkan kebutuhan untuk memiliki beberapa “salinan” IR virtual atau tahapan pipeline yang menjaga konten instruksi untuk setiap tahap. Jika sebuah instruksi di IR tahap decode menyebabkan hazard (misalnya, perlu data yang belum tersedia), seluruh pipeline mungkin harus di-stall, dan isi IR pada tahap tersebut akan “terjebak” sampai masalah terselesaikan.

Desain pipeline yang canggih bahkan memiliki mekanisme untuk membuang (flush) isi IR jika terjadi branch yang salah prediksi.

Studi Kasus dan Contoh Nyata

Mari kita ikuti perjalanan satu instruksi dari awal hingga akhir untuk melihat betapa sentralnya peran IR. Kita ambil contoh instruksi “LOAD R1, [0x100]”, yang artinya muat data dari alamat memori 0x100 ke dalam register R1, pada arsitektur sederhana.

Analisis Siklus Lengkap dan Micro-Operations

Setelah instruksi ini di-fetch dan dimuat ke dalam IR, unit kontrol mendecodenya. Opcode menunjukkan ini adalah instruksi LOAD, operand menunjukkan register tujuan R1 dan alamat memori 0x

100. Berikut urutan langkah mikro (micro-operations) yang dipicu:

- Isi IR (instruksi LOAD) telah tersedia.

- Unit kontrol mengaktifkan sinyal untuk menyalin bagian alamat dari IR ke register alamat memori (MAR).

- Unit kontrol mengaktifkan sinyal baca memori.

- Memori merespons dengan menempatkan data dari alamat 0x100 ke bus data.

- Data dari bus data disimpan ke dalam Memory Data Register (MDR).

- Unit kontrol mengaktifkan sinyal untuk menyalin data dari MDR ke register tujuan, R1.

- Siklus untuk instruksi ini selesai, PC sudah menunjuk ke instruksi berikutnya.

Perbandingan Konseptual IR dalam CISC vs RISC

Filosofi desain CISC (Complex Instruction Set Computer) dan RISC (Reduced Instruction Set Computer) membawa pendekatan berbeda terhadap IR dan proses decoding.

Proses eksekusi instruksi yang berada di register IR itu mirip seperti membaca resep kuno: ada perintah spesifik yang harus dijalankan langkah demi langkah. Nah, kalau kita tilik lebih jauh, naluri manusia untuk mengikuti pola dan instruksi ini sudah ada sejak lama, bahkan bisa dilacak dari Fungsi Ragam Hias pada Zaman Manusia Purba yang bukan sekadar estetika, melainkan kode simbolis bernilai instruktif.

Kembali ke dunia digital, register IR pun berperan serupa—menahan kode instruksi agar CPU dapat memprosesnya secara berurutan dan presisi.

Pada arsitektur CISC klasik, instruksi bisa sangat kompleks dan panjang variabel. IR seringkali berperan sebagai buffer awal. Decoding dilakukan secara bertahap (multi-cycle) dan mungkin melibatkan microcode—sebuah lapisan interpretasi di dalam CPU yang menerjemahkan instruksi kompleks menjadi serangkaian langkah mikro sederhana. IR di sini menyimpan instruksi makro yang kemudian “dijabarkan” oleh unit microcode.

Sebaliknya, pada arsitektur RISC murni, instruksi memiliki format tetap dan sederhana. Decoding dari IR menjadi sinyal kendali biasanya lebih langsung dan cepat, seringkali dilakukan secara hardwired (logika kombinasional langsung). IR menyimpan instruksi yang bentuknya sudah “ramah” untuk dieksekusi dalam satu siklus pipelined, meminimalkan kompleksitas penerjemahan.

Penutupan

Jadi, begitulah kisah singkat sang pengendali diam di dalam CPU. Proses eksekusi instruksi dari register IR mungkin terdengar teknis dan jauh dari keseharian, tetapi sesungguhnya dialah denyut nadi yang menghidupi setiap aplikasi dan game favoritmu. Memahaminya adalah seperti mengintip ke balik layar panggung pertunjukan besar teknologi, melihat konduktor yang dengan tenang mengarahkan setiap instrumen sirkuit untuk menghasilkan simfoni komputasi yang mulus.

Pada akhirnya, di balik semua kompleksitas arsitektur CISC atau RISC, prinsip dasarnya tetap sama: baca, pahami, lakukan. Sebuah mantra sederhana yang telah menggerakkan revolusi digital hingga saat ini.

FAQ dan Solusi

Apa yang terjadi jika data di register IR rusak atau tidak valid?

CPU akan mengalami kondisi kesalahan, seringkali berupa “instruction trap” atau exception. Unit kontrol tidak dapat menghasilkan sinyal yang tepat, yang bisa menyebabkan sistem hang, crash, atau menjalankan operasi tak terduga yang membahayakan stabilitas.

Apakah register IR bisa diakses langsung oleh program aplikasi?

Tidak bisa. Register IR adalah bagian dari unit kontrol CPU yang bersifat internal dan transparan bagi perangkat lunak tingkat pengguna. Programmer tidak dapat membaca atau menulis ke IR secara langsung; aksesnya dikelola sepenuhnya oleh perangkat keras CPU selama siklus instruksi.

Proses eksekusi instruksi yang berada di register IR adalah jantung dari operasi CPU, di mana setiap perintah di-decode dan dijalankan secara deterministik. Nah, dalam mempelajari konsep teknis seperti ini, pemahaman dasar bahasa Inggris—misalnya melalui Latihan Noun Countable dan Uncountable: Contoh dan Kalimat —sangat krusial untuk mengartikan dokumentasi teknis yang padat. Pada akhirnya, kejelasan konseptual ini langsung berkontribusi pada pemahaman yang lebih mendalam tentang bagaimana IR memandu eksekusi instruksi tersebut.

Mengapa lebar bit register IR berbeda-beda antar prosesor?

Lebar bit IR ditentukan oleh desain set instruksi (ISA). Prosesor dengan instruksi kompleks (CISC) cenderung memiliki IR yang lebih lebar untuk mengakomodasi format instruksi yang variatif, sementara desain RISC yang sederhana seringkali menggunakan IR dengan lebar tetap dan lebih standar untuk efisiensi dan kecepatan decoding.

Bagaimana pengaruh pipelining terhadap register IR?

Dalam CPU berpipelining, seringkali digunakan lebih dari satu “stage register” yang berfungsi seperti IR di setiap tahap pipeline (misal, IF/ID, ID/EX). Ini memungkinkan beberapa instruksi diproses secara bersamaan di tahapan yang berbeda, sehingga IR tradisional tunggal berevolusi menjadi beberapa buffer yang mengalirkan instruksi sepanjang pipeline.