Cara menyelesaikan (AVB) ∧ [(¬A) ∧ (¬B)] itu seperti mencoba memecahkan teka-teki yang dari sananya sudah mustahil. Bayangkan kamu diminta untuk memilih antara teh atau kopi, tapi di saat bersamaan dilarang memilih teh dan juga dilarang memilih kopi. Ekspresi logika ini, sekilas tampak seperti rumus biasa, namun sebenarnya menyimpan paradoks yang menarik untuk ditelusuri. Mari kita bedah bersama, bukan dengan kening berkerut, tapi dengan rasa penasaran layaknya mengamati sebuah ilusi optik yang menipu pikiran.

Pada intinya, ekspresi ini menggabungkan dua pernyataan dengan operator AND (∧). Sisi kiri, (A ∨ B), menyatakan bahwa A atau B (atau keduanya) harus benar. Sementara sisi kanan, [(¬A) ∧ (¬B)], justru bersikukuh bahwa A tidak benar dan B juga tidak benar. Konflik ini bukanlah kebetulan, melainkan sebuah kontradiksi struktural yang akan selalu menghasilkan nilai false, terlepas dari apapun nilai A dan B-nya.

Analisis kita akan membimbing kamu melalui tabel kebenaran, penyederhanaan dengan hukum logika, hingga visualisasi yang membuat kontradiksi ini menjadi jelas dalam sekejap.

Mengurai Lapisan Makna Logis dalam Ekspresi (A∨B) ∧ [(¬A) ∧ (¬B)]

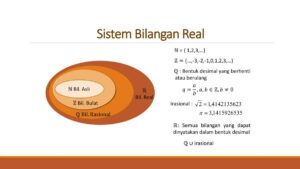

Sebelum menyelam ke dalam kompleksitas ekspresi ini, mari kita pahami fondasinya. Dalam logika proposisional, kita bekerja dengan pernyataan yang bisa bernilai benar (True) atau salah (False). Variabel A dan B mewakili pernyataan-pernyataan dasar tersebut. Interaksi mereka diatur oleh operator. Operator OR (∨) bersifat inklusif: (A∨B) akan benar jika setidaknya satu dari A atau B benar.

Sebaliknya, operator AND (∧) menuntut semua komponennya benar untuk menghasilkan nilai benar. Operator negasi (¬) membalik nilai: jika A benar, maka ¬A salah, dan sebaliknya. Ekspresi kita menggabungkan semua ini dalam sebuah struktur yang menarik, yang akan kita bedah secara bertahap.

Tabel Kebenaran Ekspresi Logika

Untuk melihat dengan jelas bagaimana ekspresi ini berperilaku, tabel kebenaran adalah alat yang paling jitu. Tabel berikut memetakan semua kemungkinan kombinasi nilai A dan B, dan mengikuti komputasi logis hingga ke hasil akhir.

| A | B | A∨B | ¬A ∧ ¬B | Hasil Akhir |

|---|---|---|---|---|

| False | False | False | True | False |

| False | True | True | False | False |

| True | False | True | False | False |

| True | True | True | False | False |

Dari tabel, terlihat sebuah pola yang konsisten: kolom hasil akhir selalu bernilai False, terlepas dari apapun nilai A dan B. Ini adalah indikasi kuat bahwa kita berhadapan dengan sebuah kontradiksi.

Penyederhanaan Menggunakan Hukum Logika

Kita dapat membuktikan bahwa ekspresi ini selalu salah tanpa harus menguji semua kombinasi, yaitu dengan menyederhanakannya menggunakan hukum-hukum aljabar Boolean. Mari kita ikuti langkah-langkahnya.

Ekspresi awal: (A ∨ B) ∧ (¬A ∧ ¬B)

Langkah 1: Terapkan Hukum Asosiatif untuk mengelompokkan.(A ∨ B) ∧ (¬A ∧ ¬B) tetap sama karena konjungsi (∧) asosiatif.

Nah, kalau kita lihat ekspresi logika (A∨B) ∧ (¬A) ∧ (¬B), penyelesaiannya bakal selalu bernilai false karena ada kontradiksi internal. Ini mirip kayak konsep dalam geometri, di mana kita mencari hubungan unik antar besaran, seperti pada pembahasan menarik tentang Sudut Besar 1/4 Kali Penyikuannya. Sama halnya, dalam logika, identifikasi kontradiksi itu kunci utamanya, sehingga solusi akhir dari pernyataan majemuk tadi sudah pasti salah.

Langkah 2: Kenali bahwa (¬A ∧ ¬B) adalah negasi dari (A ∨ B) berdasarkan Hukum De Morgan.¬A ∧ ¬B ≡ ¬(A ∨ B)

Langkah 3: Substitusi ke ekspresi awal.Ekspresi menjadi: (A ∨ B) ∧ ¬(A ∨ B)

Langkah 4: Identifikasi bentuk Kontradiksi.Bentuk X ∧ ¬X adalah sebuah kontradiksi yang selalu bernilai False, terlepas dari nilai X (yang dalam hal ini adalah (A ∨ B)).

Dengan demikian, penyederhanaan membuktikan bahwa ekspresi kita secara logis setara dengan sebuah pernyataan yang secara langsung bertentangan dengan dirinya sendiri.

Analogi Pengambilan Keputusan yang Mustahil

Bayangkan kamu sedang mempertimbangkan dua pekerjaan, sebut saja Pekerjaan A dan Pekerjaan B. Seorang penasihat yang aneh memberimu dua syarat yang harus dipenuhi bersamaan: “Kamu harus menerima setidaknya satu dari dua pekerjaan itu (A atau B).” Seketika itu juga, dia menambahkan, “Dan pada saat yang sama, kamu harus menolak kedua pekerjaan tersebut (bukan A dan bukan B).” Jelas, ini adalah sebuah permintaan yang mustahil dipenuhi.

Tidak ada kondisi di dunia nyata yang memungkinkan kamu secara bersamaan menerima setidaknya satu tawaran dan menolak keduanya. Ekspresi logika (A∨B) ∧ (¬A ∧ ¬B) adalah representasi matematis yang tepat dari skenario absurd semacam ini. Ia menggambarkan sebuah klaim yang mengandung benih kehancurannya sendiri, karena bagian kedua secara langsung menyangkal syarat yang ditetapkan oleh bagian pertama.

Visualisasi Jaringan Alur Pikir untuk Memahami Konjungsi yang Kontradiktif: Cara Menyelesaikan (AVB) ∧ [(¬A) ∧ (¬B)]

Kadang, logika yang tersusun rapi dalam simbol perlu diterjemahkan ke dalam alur agar lebih mudah dicerna. Visualisasi diagram alur membantu kita melihat konflik secara spasial, bukan hanya secara simbolik. Bayangkan dua jalur pemikiran yang berjalan paralel. Jalur pertama memproses kemungkinan (A∨B), bertindak seperti sebuah corong yang mengumpulkan semua keadaan di mana A atau B benar. Jalur kedua memproses [(¬A) ∧ (¬B)], yang berfungsi seperti filter ketat yang hanya melewatkan keadaan di mana A dan B bersama-sama salah.

Kedua jalur ini kemudian bertemu di sebuah titik pertemuan yang kritis: sebuah gerbang logika AND. Gerbang ini berperan sebagai penilai akhir yang akan memberi lampu hijau (output True) hanya jika kedua jalur yang masuk ke dalamnya sedang aktif (bernilai True) pada saat yang bersamaan. Inilah inti dari visualisasi ini. Diagram akan menunjukkan dengan jelas bahwa kedua jalur tersebut tidak pernah aktif secara simultan.

Ketika jalur pertama aktif karena A atau B benar, jalur kedua pasti mati karena syarat “bukan A dan bukan B” dilanggar. Sebaliknya, ketika jalur kedua aktif (saat A dan B sama-sama salah), jalur pertama justru dalam keadaan mati. Pertemuan di gerbang AND itu selalu berakhir dengan kebuntuan, tidak ada sinyal yang bisa lolos.

Poin-Poin Diagram Logika yang Efektif

Sebuah diagram yang dirancang untuk menjelaskan konflik ini harus memuat elemen-elemen kunci berikut agar pemahaman menjadi instan:

- Dua Jalur Input yang Terpisah Jelas: Diagram harus menunjukkan A dan B sebagai titik awal yang bercabang menjadi dua jalur pemrosesan yang independen, satu menuju operasi OR dan satu lagi menuju operasi NOT kemudian AND.

- Representasi Visual dari Negasi: Penggunaan simbol seperti lingkaran kecil (bubble) pada garis input gerbang atau blok pemroses terpisah untuk operasi NOT, guna menegaskan proses pembalikan nilai.

- Gerbang Logika yang Ditegaskan: Simbol gerbang OR (berbentuk pelengkung) dan gerbang AND (berbentuk setengah lingkaran datar) harus mudah dibedakan, dengan label yang jelas jika diperlukan.

- Titik Konvergensi yang Menonjol: Gerbang AND final harus menjadi fokus diagram, tempat kedua jalur bertemu. Warna atau highlight dapat digunakan untuk menandai titik ini.

- Indikasi Status yang Bertentangan: Diagram statis bisa menggunakan tanda centang (✓) dan silang (✗) berwarna, atau diagram dinamis dalam deskripsi mental dapat menggambarkan aliran “listrik” yang terhalang di gerbang akhir.

Ilustrasi Mental Dua Saklar dan Sebuah Pintu

Coba bayangkan sebuah ruangan dengan satu lampu. Untuk menyalakan lampu, ada sebuah sistem yang aneh. Sistem ini memiliki sebuah “Pintu Logika AND” yang harus terbuka agar daya mengalir. Kunci untuk membuka pintu ini ada dua dan harus ditekan bersamaan: Saklar S1 dan Saklar S2. Sekarang, definisikan A sebagai “Saklar Fisik 1 ON” dan B sebagai “Saklar Fisik 2 ON”.

Kondisi (A∨B) berarti “setidaknya satu saklar fisik dalam posisi ON”. Sementara itu, [(¬A) ∧ (¬B)] berarti “kedua saklar fisik dalam posisi OFF”.

Bagian yang kontradiktif: Saklar S1 dan S2 pada pintu logika justru tidak dihubungkan ke posisi saklar fisik yang sebenarnya, melainkan ke interpretasi logika tadi. Saklar S1 akan ON hanya jika kondisi (A∨B) terpenuhi. Saklar S2 akan ON hanya jika kondisi [(¬A) ∧ (¬B)] terpenuhi. Akhirnya, lampu akan menyala hanya jika S1 DAN S2 ON bersama. Dari ilustrasi sebelumnya, kita tahu S1 dan S2 tidak pernah ON bersamaan.

Maka, pintu logika itu tak pernah terbuka, dan lampu tak akan pernah menyala, persis seperti output ekspresi kita yang selalu False.

Penerapan Prinsip Negasi Ganda dan Implikasinya dalam Struktur Ekspresi

Operator negasi (¬) bukan sekadar pembalik nilai; ia adalah pembangun kompleksitas. Dengan menempatkannya secara strategis, kita dapat menyusun kalimat logika yang menyangkal kondisi tertentu. Pada ekspresi [(¬A) ∧ (¬B)], negasi bekerja pada tingkat variabel dasar, menciptakan sebuah klaim baru: “A tidak benar dan B tidak benar”. Ini adalah penegasan terhadap ketidakhadiran atau penolakan terhadap kedua kondisi awal sekaligus. Ketika sub-ekspresi ini berdiri sendiri, ia memiliki ruang kebenaran yang valid, yaitu saat A dan B memang bersama-sama salah.

Kekuatan negasi menjadi lebih terlihat ketika kita membandingkan [(¬A) ∧ (¬B)] dengan negasi dari (A∨B). Di sinilah Hukum De Morgan menunjukkan keanggunannya. Hukum ini menyatakan bahwa negasi dari sebuah disjungsi (OR) setara dengan konjungsi (AND) dari masing-masing negasinya, dan sebaliknya.

| Bentuk Asli | Bentuk Negasi (setara menurut De Morgan) |

|---|---|

| ¬(A ∨ B) | (¬A) ∧ (¬B) |

| ¬(A ∧ B) | (¬A) ∨ (¬B) |

Perbandingan ini mengungkap bahwa [(¬A) ∧ (¬B)] bukanlah sembarang pernyataan, melainkan secara logis identik dengan ¬(A∨B). Inilah kunci yang membuka kontradiksi dalam ekspresi utama kita.

Konjungsi antara Pernyataan dan Negasinya

Ketika ekspresi (A∨B) dikonjungsikan dengan ¬(A∨B), kita memasuki wilayah kontradiksi yang fundamental. Dalam aljabar Boolean, prinsip ini dikenal sebagai Hukum Kontradiksi atau Law of Non-Contradiction, yang secara formal dinyatakan sebagai X ∧ ¬X = 0 (selalu salah). Struktur ini adalah bentuk paling murni dari inkonsistensi. Tidak ada sistem penalaran yang koheren, baik dalam matematika, ilmu komputer, maupun filsafat, yang dapat menerima sebuah pernyataan dan penyangkalan terhadap pernyataan yang sama sebagai benar secara bersamaan.

Ekspresi kita, setelah disederhanakan, jatuh tepat ke dalam pola ini, menjadikannya sebuah tautologi untuk ketidakmungkinan.

Contoh penerapan prinsip ini dapat ditemukan dalam desain sistem digital sederhana, seperti circuit untuk mendeteksi kesalahan input. Bayangkan sebuah sistem yang mengharapkan dua sinyal, A dan B, tidak pernah aktif bersamaan (misalnya, dua tombol yang saling mengunci). Ekspresi pencekanya adalah (A ∧ B). Jika kita ingin lampu peringatan menyala ketika aturan ini dilanggar, kita gunakan negasi: ¬(A ∧ B). Namun, jika secara tidak sengaja kita merancang sirkuit yang mengaktifkan alarm berdasarkan logika (A ∧ B) ∧ ¬(A ∧ B), maka alarm itu tidak akan pernah berbunyi, bahkan saat kesalahan (A dan B aktif bersama) benar-benar terjadi. Ini adalah contoh nyata bagaimana kontradiksi menghasilkan sistem yang gagal berfungsi.

Eksplorasi Konteks Filosofis dari Sebuah Pernyataan yang Menjadi Batal Sendiri

Di luar dunia matematika dan sirkuit, ekspresi logika yang selalu salah ini memiliki resonansi yang dalam dengan cara kita berpikir dan berargumentasi. Ia mencerminkan struktur dari apa yang dalam retorika dan filsafat dikenal sebagai pernyataan yang membatalkan dirinya sendiri (self-defeating statement). Pernyataan semacam ini mengandung premis atau implikasi yang, jika diterima kebenarannya, justru akan meruntuhkan atau menyangkal kebenaran pernyataan itu sendiri.

Sebuah contoh klasik adalah klaim “Semua aturan memiliki pengecualian.” Jika klaim ini benar, maka harus ada pengecualian untuk aturan tersebut, yang berarti ada aturan yang tidak memiliki pengecualian, sehingga menyangkal klaim awal. Pola “X dan bukan-X” dalam logika formal adalah versi yang termurni dari fenomena ini, di mana pertentangan itu eksplisit dan tak terbantahkan.

Struktur kontradiktif semacam ini sering menjadi dasar dari berbagai kesalahan nalar, meski dalam bentuk yang lebih tersamar. Mengidentifikasinya membantu kita membersihkan argumen dari inkonsistensi.

Kesalahan Nalar dengan Struktur Serupa

- Kontradiksi Internal (Self-Contradiction): Langsung menyatakan dua hal yang saling menafikan dalam satu argumen. Contoh: “Kota ini sangat sepi dan ramai pada saat yang bersamaan di hari yang sama.”

- Menggergaji Dahan yang Diduduki (Sawing Off The Branch You’re Sitting On): Menggunakan sebuah prinsip untuk menyangkal prinsip itu sendiri, atau meruntuhkan landasan yang membuat argumenmu valid. Contoh: Seorang yang berkata “Kamu tidak boleh mempercayai siapa pun” justru memintamu untuk mempercayai pernyataannya tersebut.

- Beban Pembuktian yang Kontradiktif: Menetapkan standar pembuktian yang mustahil atau yang, jika diterapkan secara konsisten, akan membatalkan klaim si pemberi argumen sendiri. Contoh: Seorang penyangkal sejarah yang mengatakan “Semua dokumen sejarah itu dipalsukan,” namun menggunakan ketiadaan dokumen sebagai bukti; standar ini membuat klaimnya tidak dapat diverifikasi maupun difalsifikasi dengan cara apa pun.

Skenario Debat dan Hipotesis Ilmiah

![Tolong dong gimana cara ngerjainnya (AVB) ^ [(~A)^(~B)] - Brainly.co.id Cara menyelesaikan (AVB) ∧ [(¬A) ∧ (¬B)]](https://gurubaik.de/wp-content/uploads/2026/01/5039cea25d9818026d3ccffa42785c69-1.png)

Source: z-dn.net

Dalam sebuah debat tentang kebijakan, bayangkan seorang pembicara berargumen: “Solusi untuk masalah ini adalah kita harus melakukan intervensi pemerintah yang kuat (A) atau membiarkan mekanisme pasar bekerja sepenuhnya (B).” Kemudian, di titik lain, dia juga bersikeras: “Namun, pada dasarnya, intervensi pemerintah selalu buruk (¬A) dan mekanisme pasar murni juga selalu gagal (¬B).” Jika seorang lawan debat yang cermat menyatukan kedua pernyataan ini menjadi struktur logika kita, kelemahannya langsung tersingkap: si pembicara pada dasarnya mengatakan bahwa satu-satunya solusi yang diajukan (A atau B) adalah hal-hal yang dia yakini tidak akan bekerja (bukan A dan bukan B).

Argumennya runtuh karena menawarkan pilihan yang sekaligus dia tolak.

Dalam penyusunan hipotesis ilmiah, pemahaman terhadap bentuk logika kontradiktif ini penting untuk menghindari perumusan hipotesis yang tidak dapat diuji. Sebuah hipotesis yang secara logis setara dengan sebuah kontradiksi tidak akan pernah bisa memiliki bukti pendukung, karena tidak ada keadaan di dunia nyata yang dapat memenuhinya. Melatih diri untuk mendeteksi pola ini, baik yang eksplisit maupun implisit, mengasah ketajaman berpikir kritis.

Itu melatih kita untuk tidak hanya mendengar klaim, tetapi memeriksa konsistensi internalnya, menjaga agar penalaran kita tetap kokoh dan terhindar dari jebakan mengiyakan hal-hal yang pada dasarnya mustahil.

Transformasi Ekspresi Logika menjadi Sirkuit Digital Elementer dan Analisis Outputnya

Logika Boolean adalah bahasa ibu dari sirkuit digital. Setiap ekspresi dapat direalisasikan sebagai rangkaian gerbang logika. Untuk ekspresi (A∨B) ∧ [(¬A) ∧ (¬B)], kita membutuhkan tiga jenis gerbang dasar: NOT (untuk membalik sinyal), OR (untuk menjumlahkan logika), dan AND (untuk mengalikan logika). Proses konversinya langsung: kita bangun sub-sirkuit untuk (A∨B) menggunakan satu gerbang OR dengan input A dan B. Secara paralel, kita bangun sub-sirkuit untuk [(¬A) ∧ (¬B)] dengan pertama-tama menghubungkan A dan B masing-masing ke sebuah gerbang NOT untuk menghasilkan ¬A dan ¬B, lalu kedua output ini dihubungkan ke sebuah gerbang AND.

Akhirnya, output dari gerbang OR dan output dari gerbang AND tadi dihubungkan sebagai input ke sebuah gerbang AND final yang menghasilkan output ekspresi lengkap.

Perilaku sirkuit ini untuk setiap kombinasi input dapat diringkas dalam tabel kebenaran berikut, yang kini juga mencerminkan output pada titik-titik kritis (gerbang-gerbang tengah).

| Input A | Input B | Output OR (A∨B) | Output NOT A | Output NOT B | Output AND (¬A∧¬B) | Output AND Final |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 |

Aliran Sinyal dalam Sirkuit untuk Semua Kombinasi, Cara menyelesaikan (AVB) ∧ [(¬A) ∧ (¬B)]

Mari kita lacak aliran listrik (direpresentasikan sebagai logika 1) secara deskriptif. Saat A=0 dan B=0, gerbang OR tidak mendapat sinyal ‘tinggi’, sehingga outputnya 0. Di jalur paralel, kedua gerbang NOT membalik 0 menjadi 1, sehingga gerbang AND tengah mendapat dua sinyal 1 dan outputnya menjadi 1. Gerbang AND final kini menerima input 0 dari jalur OR dan 1 dari jalur AND tengah.

Karena syarat AND adalah semua input harus 1, gerbang ini memblokir aliran dan output akhir tetap 0.

Untuk tiga kombinasi lainnya (0,1; 1,0; 1,1), gerbang OR akan selalu menghasilkan output 1 karena setidaknya satu inputnya tinggi. Namun, di jalur paralel, kondisi ini menyebabkan setidaknya satu dari ¬A atau ¬B bernilai 0. Misal, jika A=1, maka ¬A=0. Input 0 ke gerbang AND tengah langsung mematikan outputnya menjadi 0, terlepas dari nilai input lainnya. Jadi, gerbang AND final selalu menerima pasangan input (1,0) atau (1,0) atau (1,0) pada kasus terakhir.

Pasangan mana pun yang terjadi, keberadaan sebuah 0 sudah cukup untuk membuat gerbang AND final terkunci, menghasilkan output 0.

Langkah Pemeriksaan Fault pada Sirkuit

Jika dalam praktiknya sirkuit hipotetis ini memberikan output 1 (yang secara teori mustahil), maka pasti terjadi kesalahan. Berikut adalah poin-poin pemeriksaan sistematis yang dapat dilakukan:

- Verifikasi Tabel Kebenaran Teoritis: Pastikan lagi bahwa pemahaman terhadap ekspresi logika dan tabel kebenarannya sudah benar, untuk mengeliminasi kesalahan konsep sebelum menyentuh perangkat keras.

- Pemeriksaan Koneksi Fisik: Periksa apakah ada koneksi yang terlepas, short circuit (hubungan pendek), atau solderan yang tidak sempurna yang dapat menyebabkan sinyal mengalir ke jalur yang tidak seharusnya.

- Pengujian Individual Gerbang: Uji setiap gerbang logika (NOT, OR, AND) secara terpisah dengan memberikan kombinasi input yang diketahui dan memverifikasi outputnya sesuai datasheet. Sebuah gerbang yang rusak dapat menghasilkan sinyal tetap tinggi (stuck-at-1) atau tetap rendah (stuck-at-0).

- Trace Sinyal dengan Multimeter atau Logic Probe: Untuk kombinasi input tertentu (misal A=0, B=0), ikuti jalur sinyal dari input hingga output, mengukur tegangan pada setiap titik (input/output gerbang). Titik di mana pengukuran menyimpang dari nilai yang diharapkan berdasarkan tabel kebenaran menandai lokasi fault.

- Review Desain PCB atau Breadboard: Periksa kemungkinan kesalahan dalam penempatan komponen (misal, gerbang AND tertukar dengan gerbang OR) atau kesalahan dalam routing jalur yang menyebabkan sinyal dari satu jalur masuk ke jalur lain secara tidak sengaja (crosstalk).

Ringkasan Akhir

Jadi, setelah mengikuti seluruh penjelasan, terlihat jelas bahwa menyelesaikan (AVB) ∧ [(¬A) ∧ (¬B)] pada akhirnya adalah tentang mengenali sebuah jalan buntu yang elegan. Ekspresi ini, meski terlihat rumit, selalu bernilai false. Pelajaran yang bisa diambil jauh melampaui sekadar aljabar Boolean. Ini adalah latihan fundamental untuk mengasah mata dalam melihat inkonsistensi, baik dalam kode program, argumen debat, maupun pengambilan keputusan sehari-hari.

Dengan memahami bentuk kontradiksi seperti ini, kita membekali diri dengan detektor logika internal yang akan berbunyi setiap kali menemui pernyataan yang membatalkan dirinya sendiri.

Pertanyaan yang Kerap Ditanyakan

Apakah ekspresi ini pernah memiliki nilai true?

Tidak pernah. Berdasarkan tabel kebenaran dan hukum logika, hasil akhir dari ekspresi ini selalu false untuk semua kombinasi nilai A dan B.

Bagaimana jika kita mengganti operator OR (∨) dengan AND (∧) di bagian kiri?

Jika ekspresinya menjadi (A ∧ B) ∧ [(¬A) ∧ (¬B)], kontradiksi tetap ada dan hasilnya juga selalu false. Inti kontradiksinya adalah klaim “A dan B benar” yang bertentangan dengan “A dan B salah”.

Apa kegunaan praktis mempelajari ekspresi yang selalu salah ini?

Sangat berguna, terutama dalam pemrograman dan desain sirkuit digital. Ekspresi semacam ini bisa digunakan untuk mengidentifikasi bug, memeriksa kondisi yang tidak mungkin terjadi, atau bahkan sengaja digunakan untuk mereset suatu kondisi ke nilai false.

Apakah bentuk seperti ini termasuk logical fallacy?

Ya, strukturnya mirip dengan fallacy yang dikenal sebagai “kontradiksi” atau “inconsistency”, di mana premis-premis yang diajukan saling meniadakan sehingga kesimpulan apa pun menjadi tidak valid.